AMD đã xác nhận các chi tiết mới về công nghệ 3D V-Cache mới của họ được sử dụng bởi dòng Ryzen 7000X3D.

Đã gần một tuần kể từ ngày ra mắt dòng Ryzen 7000X3D. AMD cũng đã phát hành một bộ tài liệu mở cho những người đánh giá và cung cấp tất cả các chi tiết cần thiết mà người tiêu dùng có thể muốn biết. Vẫn còn một số chi tiết về 3D V-Cache có thể không quan trọng đối với người dùng bình thường, nhưng sẽ là thông tin rất thú vị đối với cộng đồng công nghệ.

Cuối tuần qua, AMD đã cung cấp thêm thông tin chi tiết về công nghệ 3D V-Cache cũng như công bố bức ảnh đầu tiên về khuôn I/O mới, chiplet đời thứ ba đi kèm với CPU 8 nhân kép có tên mã là Raphael.

Thông tin chi tiết này đã được cung cấp cho Tom’s Hardware, trong khi các chi tiết còn lại đã được xác nhận trong Hội nghị Mạch thể rắn Quốc tế 2023 (International Solid-State Circuits Conference – ISSCC).

3D V-Cache trên dòng Ryzen 7000 mở rộng bộ đệm cấp 3 lên tới 96 MB cho một trong các chiplet. Bản thân Bộ nhớ đệm được thiết kế trong quy trình 7nm, trong khi nó được đặt trên CCD Zen4 5nm.

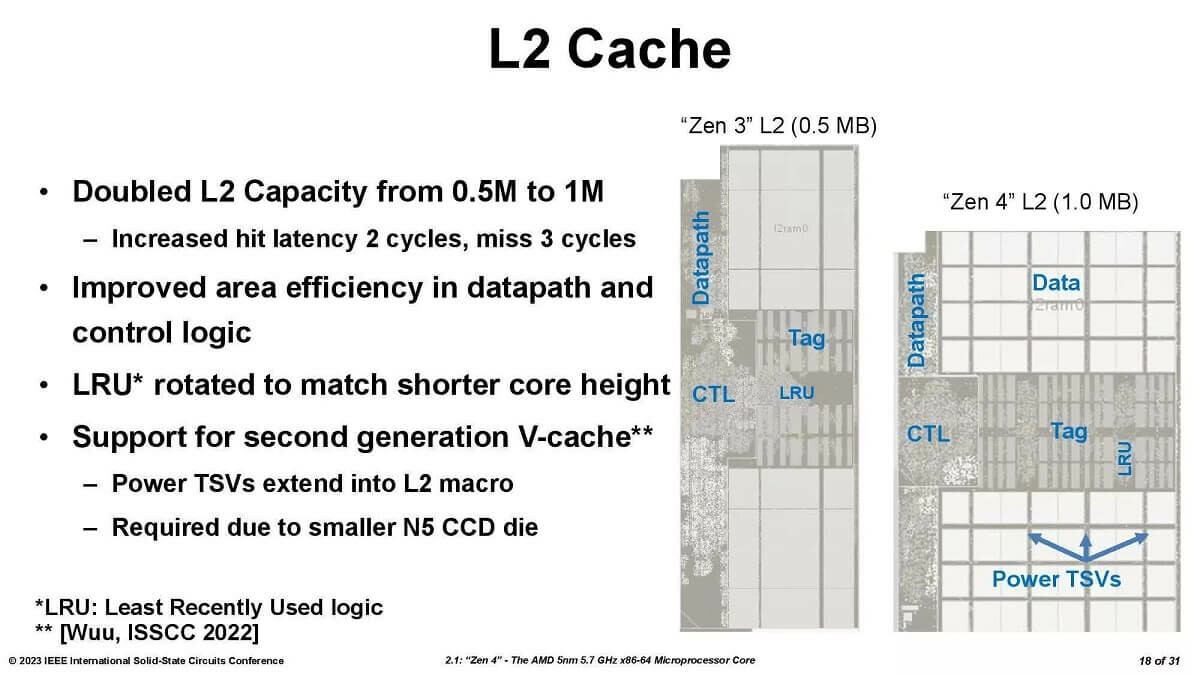

Khuôn bộ đệm thế hệ thứ hai thực sự nhỏ hơn thế hệ thứ nhất, trong khi vẫn giữ nguyên số lượng bóng bán dẫn. Điều này có nghĩa là mật độ bóng bán dẫn đã tăng từ 114,6M lên 130,6MTr/mm².

AMD cũng đã xác nhận rằng Bộ nhớ đệm 3D V-Cache mới có băng thông cao hơn, đạt tới 2,5 TB/s. Đó là sự cải thiện 25% hay 0,5 TB/s so với thiết kế khuôn bộ đệm AMD Ryzen 7 5800X3D.

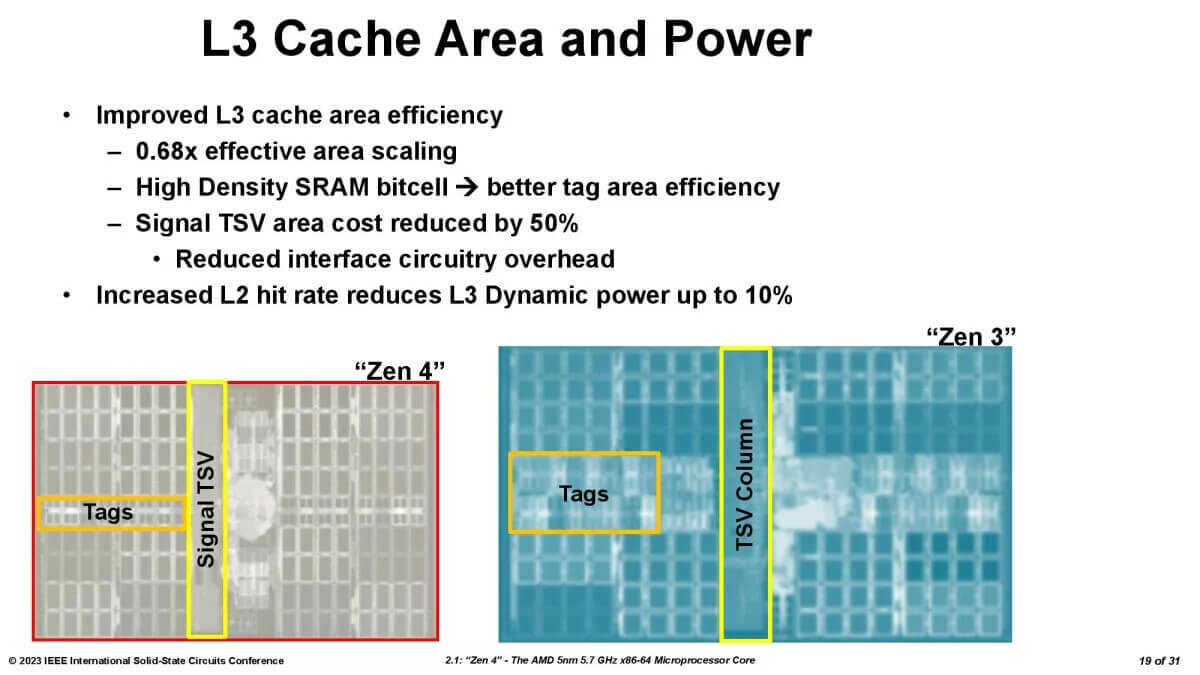

Hơn nữa, do những thay đổi trong thiết kế, AMD cũng phải thay đổi các kết nối TSV (Through Silicon Vias). AMD đã phải thu nhỏ 50% diện tích TSV.

AMD đang sử dụng cùng một CCD Zen4 trên dòng Ryzen và EPYC, nhưng khuôn I/O đã được sửa đổi cho phù hợp với người tiêu dùng và môi trường trung tâm dữ liệu. Hình ảnh về khuôn I/O của người tiêu dùng cũng đã được chia sẻ với bản trình chiếu.

Thông tin độc đáo này đã được thêm vào bản trình bày của ISSCC và nhanh chóng được phân tích bởi thám tử phần cứng Locuza, người đã cung cấp các chú thích thích hợp. Nó cho thấy GPU tích hợp lớn như thế nào và xác nhận rằng nó thực sự bị giới hạn ở 128 lõi.

Họ cũng xác nhận thêm rằng khuôn I/O chỉ có hai cổng GMI (Global Memory Interconnect – Kết nối bộ nhớ toàn cầu), do đó không thể có cấu hình ba CCD với chiplet này.